Poster Session II

EDP2-1

Sharpening and characterizing of YBa2Cu3O7-δ probes for scanning probe microscopy

13:15-14:45 Dec.4

*B.Ohnishi1, R. Taguchi1, K. Hayashi, S. Tanaka1, Y. Miyato2, N. Hiroshiba3, S. Ariyoshi1

Toyohashi University of Technology, Tempaku-cho, Toyohashi, Aichi, 441-8580, Japan1

Ryukoku University, Seta Oe-cho, Otsu, Shiga, 520-2194, Japan 2

Osaka Institute of Technology, Asahi-ku Omiya, Osaka, Osaka, 535-8585, Japan3

New functional probes in scanning probe microscopy (SPM) are powerful tools for understanding nanoscale phenomena. The purpose of this study is to develop new measurement methods for SPM and to realize tunnel junctions with a high-temperature superconductor (HTS) probe. Currently, various materials such as tungsten and silicon are used for SPM probes, but no measurements have been made with YBa2Cu3O7-δ (YBCO) probes, which lead to an SPM measurement method using the multiple Andreev reflections [1,2]. Furthermore, controllable formation of the tunnel junction is expected by bringing the sharped probe and sample close to each other.

In the fabrication of the probe, one end of the YBCO rod was sharpened by fine cutter machine and focused ion beam, where c-axis orientation and crystallinity of the YBCO bulk were confirmed by X-ray diffraction measurements [3]. As a result of the condition optimization, a sharp shape with 88.5 nm radius of curvature.

In the evaluation of the probe, the resistance-temperature characteristics of the YBCO were evaluated, and the transition temperature was confirmed to be 88.6 K. The Ga distribution around the probe tip was measured before and after milling, and a decrease in Ga concentration was observed after 10 minutes of milling. Furthermore, current-voltage curves of the fabricated YBCO probes were acquired in liquid nitrogen-cooled SPM systems. In this paper, we will report detailed results including electrical properties of the YBCO probe tip and show the possibility of HTS tunnel junctions using the probes.

[1] E. N. Bratus et al., Phys. Rev. Lett., Vol 74, pp. 2110-2113, 1995.

[2] R. Hiraoka, et al., Phys. Rev. B., Vol .90, p. 241405, 2014.

[3] S. Ariyoshi, A. Ebata, B. Ohnishi, et al., IEEE Trans. Appl. Supercond., Vol. 33, No.5, p.7200104, 2023.

Keywords: Scanning probe microscopy, YBa2Cu3O7-δ (YBCO), Tunnel junction

EDP2-2

Wirebond impedance matching of superconducting qubits

13:15-14:45 Dec.4

*Qingling Zhu, Hong Su

University of Science and Technology of China

High fidelity and fast readout of qubit states are crucial for quantum computation and communication, as well as the premise of quantum error correction. Dispersive readout is widely used for superconducting qubits, and the leakage rate of the readout resonator significantly affects the readout time and reset speed, especially the multi-round readout efficiency of quantum error correction. Currently, impedance mismatch at the wirebond interface is the main cause of significant fluctuations in the leakage rate of the readout resonator[1]. To address this issue, we propose an impedance matching technology that is compatible with current packaging technology and highly scalable, which can control the fluctuation of the leakage rate of the readout resonator within 20%.

EDP2-3

Speed-Up and Delay Time Stabilization in Superconductor-Based Random Number Generation

13:15-14:45 Dec.4

*Rikuo Yamanaka1, Nobuyuki Yoshikawa1,2,3 and Yuki Yamanashi1,2,3

Department of Electrical and Computer Engineering, Yokohama National University, 79-5 Tokiwadai, Hodogaya, Yokohama, Kanagawa, 240-8501 & Japan1

Institute of Advanced Sciences, Yokohama National University, 79-5 Tokiwadai, Hodogaya, Yokohama, Kanagawa, 240-8501 & Japan2

Institute for Multidisciplinary Sciences, Yokohama National University, 79-5 Tokiwadai, Hodogaya, Yokohama, Kanagawa, 240-8501 & Japan3

Random number generators are indispensable circuits for applications such as cryptography and probabilistic computation. Superconductor-based random number generators (SRNGs) based on single-flux-quantum (SFQ) circuits are very powerful circuits for such applications because of their ultrahigh speed and compactness. While SRNGs have a very simple circuit configuration because they do not need to amplify noise, they also have the problem of unstable delay times. This makes the design of application circuits difficult and has negative effects such as a reduction in the overall throughput of the circuit.

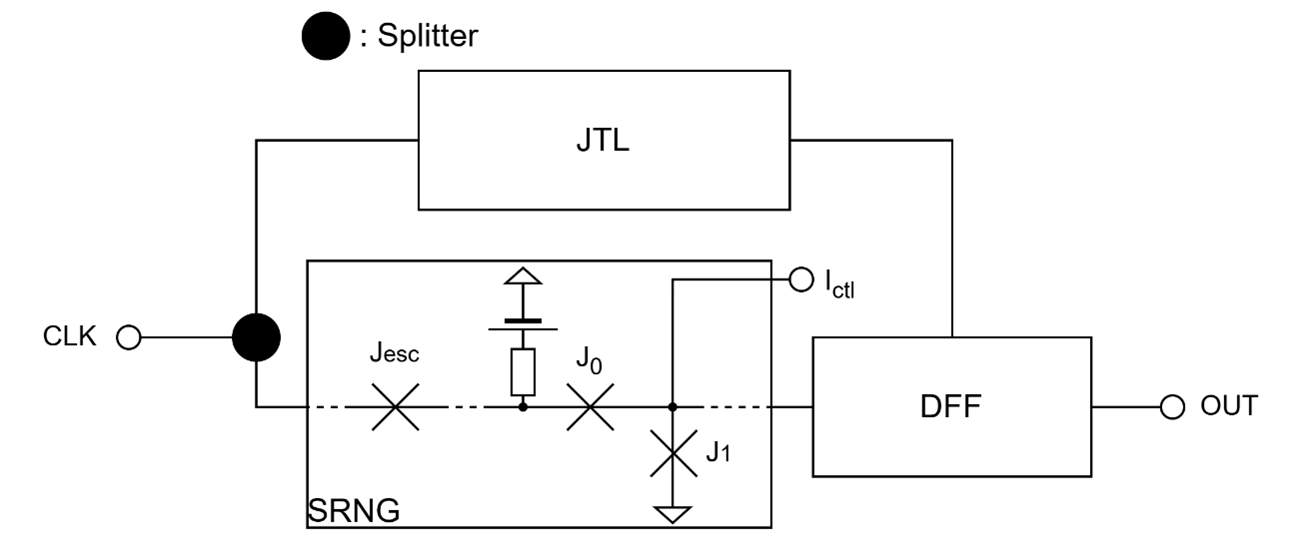

In this study, we optimized the circuit to stabilize the delay time of the SRNG as well as to reduce the delay time. Fig.1 shows the block diagram of the proposed circuit. One of the causes of delay variation is that when 1 is output, sometimes only J1 switches and sometimes both J1 and J0 switch. Therefore, in this study, the bias to the two Josephson junctions (JJs) was increased so that both JJs switch when all 1 are output, and Jesc is the JJ that prevents backflow of magnetic flux quantum when both JJs switch (when 1 is output). To further stabilize the delay, a Delay Flip-Flop (DFF) was connected to the output of the SRNG and adjusted so that the clock is input at the appropriate timing. To decrease the delay time, the driving power of the circuit was increased by increasing the bias and the critical current value of JJ in the front stage of the comparator (J1 and J0). the circuit was designed assuming an AISE 10 kA/cm^2 Nb high-speed process [2]. Simulations with thermal noise at 4.2 K using an analog circuit simulator reduced the maximum delay of the SRNG from 44.1 ps to 25.2 ps and the minimum delay from 26.0 ps to 23.6 ps. This result shows that the delay variation, which has been an issue with SRNGs, was reduced from 18.1 ps to 1.6 ps.

The delay variation of SRNGs was made close to that of general logic gates. This facilitates the design of application circuits for cryptography and probabilistic computation, etc. It is also expected to dramatically improve the overall throughput and maximum operating frequency of application circuits.

[1] Y. Yamanashi and N. Yoshikawa, “Superconductive Random Number Generator Using Thermal Noises in SFQ Circuits,” IEEE Trans. Appl. Supercond., vol. 19, no. 3, pp. 630–633, Jun. 2009.

[2] M. Hidaka and S. Nagasawa, “Fabrication process for superconducting digital circuits,” IEICE Trans. Electron., vol. E104–C, pp. 405–410, Sep. 2021.

This work was supported by KAKENHI 22H01542 and 24H00311.

Figure 1. Block diagram of circuit for stabilizing and speeding up SRNG.

Keywords: SFQ circuit, Random number generator

EDP2-4

Vapor HF etching technique for superconducting quantum circuits

13:15-14:45 Dec.4

*HIROTAKA TERAI, Satoru Mima, Mai Setoura, Kazuyo Takaki, Shigehito Miki

National Institute of Information and Communications Techonology (NICT)

Al/AlOX/Al junctions are widely used in superconducting qubits because of their easy fabrication using electron beam lithography and shadow evaporation and the stability of AlOX tunnel barrier. However, AlOX is an amorphous oxide, which is well-known decoherence source in superconducting qubits. We have developed superconducting qubits based on NbN/AlN/NbN epitaxial junctions as an alternative Josephson junction to Al/AlOX/Al junctions to suppress decoherence caused by two-level systems in amorphous AlOX tunnel barrier. The fabrication process of submicron NbN/AlN/NbN epitaxial junctions has been established and it has been demonstrated that coherence times exceeding 20 us can be achieved using this junction technology [1,2]. However, superconducting quantum circuits using NbN/AlN/NbN tri-layer stacks require an amorphous SiO2 sacrificed layer deposited by sputtering or plasma-enhanced chemical vapor deposition to isolate the base electrode from the wiring layer, while the amorphous SiO2 film is a lossy dielectric. To avoid qubit decoherence due to this lossy dielectric, the SiO2 sacrificed layer must be removed at the final step of the fabrication process. We have so far employed wet etching using a buffered HF solution to remove the SiO2 layer, but this process sometimes results in etching residue around the qubit that are thought to be composed of silicic oxide, which can cause decoherence. And this wet etching process sometimes leads to stiction due to the surface tension of the rinse solution. To solve this problem, vapor HF etching was introduced to remove the SiO2 sacrificed layer [3]. The generation of particles composed of silicic oxides was minimized by adopting appropriate etching conditions. Coplanar waveguide (CPW) resonators was fabricated with a signal line width of 10 um and a gap between the signal line and the ground plane of 6 um, where the ground plane was connected by airbridges consisting of NbTiN wiring layer. The resistance between signal line and ground plane in the CPW resonators fabricated with wet etching using buffered HF was below 1 kohm due to the stiction between the signal line and the airbridges, while the resistance for the CPW resonator fabricated with vapor HF was above 10 kohm. This indicates that the airbridges fabricated with vapor HF showed no electrical shorts between the signal lines and the airbridges due to stiction. And we also confirmed that the etching process using vapor HF does not affect the properties of the NbN/AlN/NbN epitaxial junctions at all. These results suggest that vapor HF etching technique is effective for realizing superconducting quantum circuits with multi-layer wiring.

[1] W. Qiu et al., Appl. Phys. Exp. 13,126501, 2020.

[2] S. Kim et al., Comms. Mater., 2:98, 2021.

[3] H. Dunsworth et al., Appl. Phys. Lett. 112, 063502, 2018.

This work is supported by JST Moonshot R&D (JPMJM2067) and MEXT Q-LEAP (grant no. JPMXS0118068682).

EDP2-5

Design of Stochastic Number Splitter for Single Flux Quantum Stochastic Computation Using Superconductive Random Number Generators

13:15-14:45 Dec.4

*Kaito Asaka1, Nobuyuki Yoshikawa2,3,4, Yuki Yamanashi2,3,4

Graduate School of Engineering Science, Yokohama National University, 79-5 Tokiwadai, Hodogaya, Yokohama, Kanagawa, 240-8501 & Japan1

Department of Electrical and Computer Engineering, Yokohama National University, 79-5 Tokiwadai, Hodogaya, Yokohama, Kanagawa, 240-8501 & Japan2

Institute of Advanced Sciences, Yokohama National University, 79-5 Tokiwadai, Hodogaya, Yokohama, Kanagawa, 240-8501 & Japan3

Institute for Multidisciplinary Sciences, Yokohama National University, 79-5 Tokiwadai, Hodogaya, Yokohama, Kanagawa, 240-8501 & Japan4

In stochastic computing, a number expressed as a probability of existence of '1' in a binary number sequence is used. This computation method enables us to perform multiplication and addition with a small number of logic gates. Stochastic computing is gaining attention in application fields where approximate calculations are effective, such as wireless signal processing and neural networks. However, stochastic calculation needs long computation time compared to the normal deterministic computation because it deals with long binary number sequences. We think the use of superconducting single flux quantum (SFQ) circuits, capable of high-speed operation, is a promising solution.

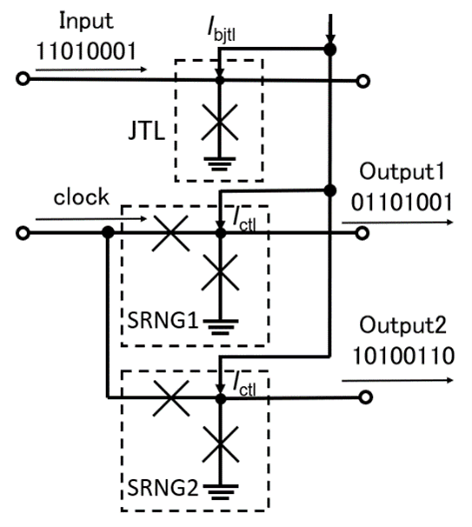

One of problems in stochastic computing is the unavoidable computational error due to correlation between the binary number sequences. If there is a correlation between the binary number sequences to be calculated, correct calculation results will not be obtained. In the single-flux-quantum (SFQ) circuit design, a splitter tree is commonly used to realize multiple fan-outs of signal splitting. However, this is not applied to the stochastic arithmetic circuit design because of the problem caused by the correlation of split number sequences. In this study, we propose the stochastic number splitter using superconducting random number generators (SRNGs) [1] and frequency synchronization [2] to solve this problem and design an efficient single-flux-quantum (SFQ) stochastic arithmetic circuit. We employ parallelly aligned n SRNGs to achieve a fan-out of n. By synchronizing the frequency of the input data line with the parallelized SRNGs, each SRNG produces a random number sequence with a probability of ‘1’s identical to that of the input number sequence. Because the output number sequences are generated by SRNGs, the output number sequences are not correlated with each other. Moreover, since the SRNGs can be implemented with the small number of Josephson junctions, the circuit area of the proposed stochastic number splitter is small.

We designed the stochastic number splitter using the AIST 10 kA/cm2 Nb high-speed standard process [3]. Analog circuit simulation results show that uncorrelated number sequences that has the probability of ‘1’s the same as that of the stochastic number sequence could be obtained. To evaluate the accuracy of the stochastic arithmetic circuit with the designed stochastic number splitter, we compared the multiplication result f(x) = x2, where x is the input stochastic number, that can be calculated with one AND gate. x is split by the designed stochastic number splitter and input to the AND gate. Assuming the 10 GHz operation of the circuit, we evaluated the calculation error by measuring mean squared error between the theoretical and simulated calculation results for the input number x of 0.0, 0.1, 0.2, ..., and 1.0. The mean squared error was reduced by an average of 76% for 256 bits and 94% for 4096 bits, compared to the mean squared error of the Flip-Flop-based bit-shift type stochastic number replicator [4]. Additionally, through simulations, we confirmed that the stochastic number splitter circuit is capable of high-speed operation up to approximately 45 GHz. In the presentation, we will discuss the measurement results of the fabricated chip.

We believe this is the first report of a high-precision stochastic number splitter using random number generators, not only for SFQ circuits but for all stochastic computing circuits. The designed stochastic number splitter is expected to be useful in various application fields requiring signal splitting, such as wireless signal processing, neural networks, image processing, and machine learning.

[1] Y. Yamanashi and N. Yoshikawa, “Superconductive Random Number Generator Using Thermal Noises in SFQ Circuits” IEEE Trans. Appl. Supercond., vol. 19, no. 3, pp. 630–633, Jun. 2009.

[2] Y. Yamanashi, R. Kinoshita and N. Yoshikawa, “Frequency synchronization od single flux quantum oscillators” Supercond. Sci. Technol. vol. 34, 105004, Sep. 2021.

[3] M. Hidaka and S. Nagasawa, “Fabrication process for superconducting digital circuits,” IEICE Trans. Electron., vol. E104–C, pp. 405–410, Sep. 2021.

[4] K. Parhi and Y. Liu, “Computing arithmetic functions using stochastic logic by series expansion” IEEE Trans. Emerg. Top. Comput., vol. 7, no. 1, pp. 44–59, Oct. 2016.

This work was supported by KAKENHI 22H01542 and 24H00311. The authors thank Naoki Ishikawa for fruitful discussion. The circuits were fabricated in the clean room for analog-digital superconductivity (CRAVITY) of National Institute of Advanced Industrial Science and Technology (AIST) with the high-speed standard process (HSTP).

Figure 1. Block diagram of the stochastic number splitter represents the bias current to the JTL, and represent the control currents to SRNGs.

Keywords: SFQ circuit, stochastic computing

EDP2-6

Development of High-Speed and Versatile Circuit Parameter Optimization Tool for Superconductor Circuits

13:15-14:45 Dec.4

*Sho Matsuoka1, Nobuyuki Yoshikawa1,2,3 and Yuki Yamanashi1,2,3

Department of Electrical and Computer Engineering, Yokohama National University, 79-5 Tokiwadai, Hodogaya, Yokohama, Kanagawa, 240-8501 & Japan1

Institute of Advanced Sciences, Yokohama National University, 79-5 Tokiwadai, Hodogaya, Yokohama, Kanagawa, 240-8501 & Japan2

Institute for Multidisciplinary Sciences, Yokohama National University, 79-5 Tokiwadai, Hodogaya, Yokohama, Kanagawa, 240-8501 & Japan3

Superconductor integrated circuits are becoming increasingly vital in advanced technological applications. As these circuits scale up, ensuring their reliable operation becomes critical despite inherent parameter variations. Therefore, designing circuits with robust tolerance to these deviations is essential, and this is where automated optimization tools play a crucial role.

There are various optimization tools for single flux quantum (SFQ) circuits, which take a long optimization time due to old simulation tools, programming languages, and optimization algorithms. These optimization tools have also been developed for the traditional SFQ circuits. In recent years, superconductor circuits have been proposed that do not use switching of junctions or 2π phase change [1], [2], which is different from the conventional SFQ circuits. Conventional optimization tools cannot be used directly on these circuits.

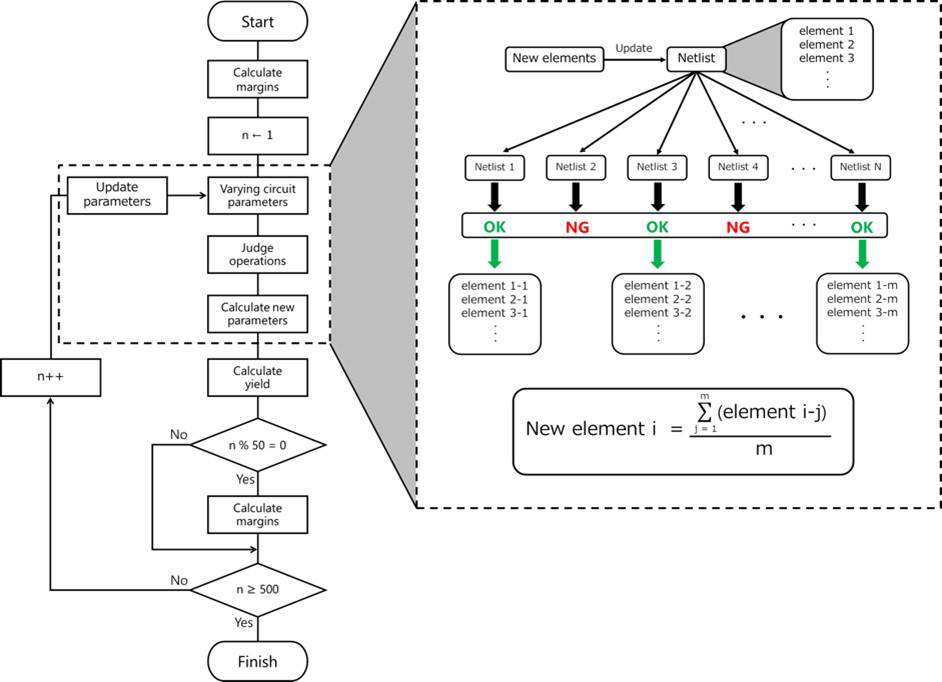

In this study, we present MarginX, a novel, simple, and rapid circuit parameter optimization tool designed for superconductor circuits composed of various types of Josephson junctions (JJs). MarginX was originally developed for extracting circuit parameter margins of SFQ circuits with normal (0-) and π-shifted JJs [3]. We have now enhanced MarginX to include circuit parameter optimization. By utilizing the time dependence of the JJ phase to determine correct operation, MarginX is applicable to both DC- and AC-biased superconductor circuits.

We optimized several SFQ logic gates and compared the optimization results and calculation time with other optimization tools. The calculation time required for the SFQ logic gate is less than 3% of that of the other optimization tools in most cases. We demonstrated the margin expansion of the half flux quantum circuit composed of both normal (0-) and π-shifted Josephson junctions. We also demonstrated optimization of adiabatic quantum flux parametron buffer [1] as an example of an AC- biased superconductor circuit. We believe MarginX is a valuable tool for designing various types of superconducting circuits.

[1] N. Takeuchi, D. Ozawa, Y. Yamanashi, and N. Yoshikawa, “An adiabatic quantum flux parametron as an ultra-low-power logic device,” Supercond. Sci. Technol., vol. 26, no. 3, p. 035010, Mar. 2013.

[2] T. Kamiya, M. Tanaka, K. Sano, and A. Fujimaki, “Energy/Space- Efficient Rapid Single-Flux-Quantum Circuits by Using π-Shifted Josephson Junctions,” IEICE Trans. Electron., vol. E101-C, no. 5, pp. 385–390, May 2018.

[3] Y. Yamanashi, S. Nakaishi, and N. Yoshikawa, “Simulation of the Margins in Single Flux Quantum Circuits Containing π-Shifted Josephson Junctions,” IEEE Trans. Appl. Supercond., vol. 29, no. 5, p. 1301805, Aug. 2019.

This work was supported by JSPS KAKENHI Grant Number JP22H01542 and JP24H00311. The authors thank Sotaro Nakaishi for developing the initial version of MarginX.

Figure 1. The optimization flowchart of MarginX. In one iteration, Ν (default value is 100) netlists with all circuit parameters randomly varied are created and the yield is calculated. The new circuit parameters are updated to the average of the parameters of the successfully operating circuit in every iteration. m is the sum of the successfully operating circuits. The default value of iteration n = 500.

Keywords: superconductor integrated circuits, margin, optimization, center of gravity method

EDP2-7

Proposal of superconducting optical input interface for a single flux quantum circuit based on pulse position modulation

13:15-14:45 Dec.4

*Shigeyuki Miyajima, Shigehito Miki

Advanced ICT Research Institute, NICT, 588-2, Iwaoka, Kobe 651-2492 Japan

Single flux quantum (SFQ) circuits are superconducting digital circuits operating at tens of GHz with low power consumption and low timing jitter, which has been developed for high-end computing [1] or cryogenic post signal processor for superconducting detectors [2]. While high-speed operation of the SFQ circuits is demonstrated for various applications, coaxial cables are usually used for input or output interfaces between room-temperature electronics and cryogenic-temperature devices, which limits the bandwidth of signals and increases in heat inflow from room temperature. An optical fiber is good candidate for input or output interfaces due to wider bandwidth with less thermal conductivity.

A superconducting strip photon detector (SSPD) is suitable for the energy efficient input interface of the SFQ circuits because the SSPDs generate an electrical pulse by illumination of a single photon with an optical fiber coupled. Also, SSPDs have some features such as high detection efficiency, low timing jitter, and low power dissipation compared to semi-conductor photo diodes [3]. However, the typical repetition frequency is a few tens of MHz, which is not fast bitrate for the input interface of SFQ circuits.

In this work, we propose a superconducting optical input interface using SSPD based on pulse position modulation (PPM), which provides input bit patterns for SFQ digital circuits. Since a bit stream is generated by the input pulse timing position relative to the start timing in PPM encoding, the SFQ time-to-digital converter (TDC) connected with SSPD is employed for PPM configuration. In this configuration, trigger signals from pulsed laser oscillator for SSPDs and output signals from SSPDs correspond to start signal and stop signal for SFQ-TDC, respectively. The length of bit stream generated by PPM technique is determined by slot time (time resolution of TDC) and frame time (full scale time of TDC). The low timing jitter of SSPDs and SFQ circuits can reduce the slot time to a few tens ps, which enhance the number of bits. Thus, the proposed system can improve bit rate for input signal without reducing response time of SSPDs.

We investigated the relationship between the bitrate and slot time with frame time of proposed OE interface. Also, we designed the SFQ-TDC for demonstration of the proposed OE interface. The designed circuit is composed of a magnetically-coupled (MC-) DC/SFQ converter [4], an internal clock generator, a 4-bit counter based on toggle flip flops (TFFs), and a 4-bit shift register as a parallel-to-serial converter. The SFQ circuits was designed based on the fabrication process with critical current density (Jc) of 10 kA/cm2 for Josephson junction (JJ). In this design, the slot time corresponding a period of clock signals by internal clock generator was set to be 250 ps, which is longer than timing jitter of SSPDs. We plan to design the SFQ digital circuits using input bit stream pattern based on proposed optical input interface.

[1] M. Tanaka, Y. Yamanashi, N. Irie, H-J. Park, S. Iwasaki, K. Takagi, K. Taketomi, A. Fujimaki, N. Yoshikawa, H. Terai, and S. Yorozu, Supercond. Sci. Technol., 20, S305 (2007)

[2] S. Miyajima, M. Yabuno, S. Miki, S. Nagasawa, M. Hidaka, and H. Terai, Appl. Phys. Lett., 122, 182602 (2023)

[3] G. N. Gol’tsman, O. Okunev, G. Chulkova, A. Lipatov, A. Semenov, K. Smirnov, B. Voronov, A. Dzardanov, C. Williams, and R. Sobolewski, Appl. Phys. Lett. 79, 705 (2001).

[4] H. Terai, T. Yamashita, S. Miki, K. Makise, and Z. Wang, Opt. Express 20, 20115 (2012).

The circuits were fabricated in the Superconducting Quantum Circuit Fabrication Facility (Qufab) in National Institute of Advanced Industrial Science and Technology (AIST).

Keywords: single flux quantum circuit, superconducting strip photon detector, pulse position modulation, optical input interface

EDP2-8

Chaotic behaviour in intrinsic Josephson junction toward high speed random number generator

13:15-14:45 Dec.4

*Dai Oikawa1, Hitokazu Komatsu2, Keita Tsuzuki1, Hiroya Andoh1, Takehiko Tsukamoto1

National Institute of Technology, Toyota College1

Kindai University2

The configuration of a high-quality security system high quality random number generator has been expected. Here, high- quality random numbers mean the numbers are random, un- reproducible and unpredictable. Until recently, random numbers have been generated from pseudo random number generators. However, the pseudo random numbers are concerned had a reproducibility issue because these numbers were dependent on the initial condition of the algorithm. Conversely, using physical randomness phenomena, such as thermal noise and non-linear electronic circuits, high-quality random number generators are produced. Specially, Chaos in physical phenomena is an appropriate random-number generator. It is known that JJ under irradiation radio frequency (RF) output chaotic voltage oscillation[1]. Here, conventional RF is roughly several tens GHz.

In this study, we numerically investigated the chaotic voltage of Josephson junction (JJ) under irradiation high frequency than conventional RF for high-quality random number generators using the equivalent circuits of JJ. Particularly, first, we will optimize the parameters when chaotic voltage appears under irradiation high frequency than conventional frequency. Thereafter, random numbers are generated from output voltage of JJ and the quality of randomness are evaluated using statistical test.

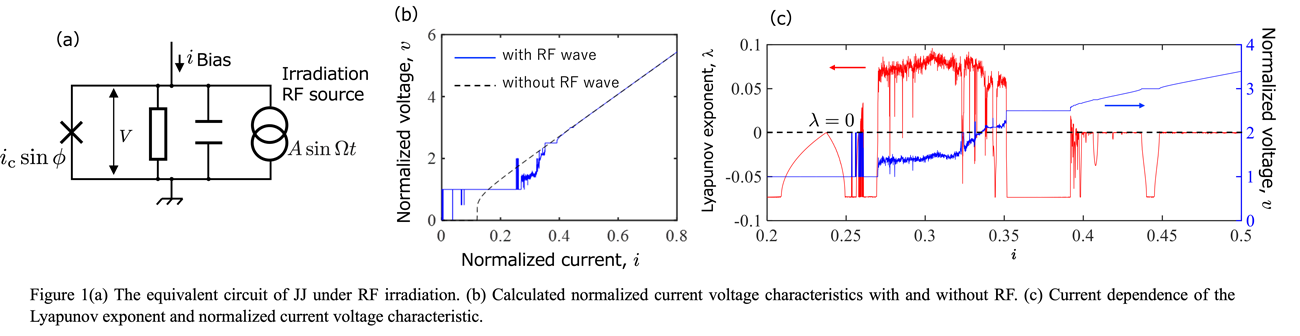

For the numerical simulation of the chaotic behavior in JJ, we adopted the equivalent circuit of RF-irradiated JJ using a resistively and capacitively shunted junction (RCSJ) model, as shown in Fig.1(a). Figure 1(b) shows calculated normalized current-voltage characteristics of JJ with and without RF. The Shapiro steps appeared on current-voltage characteristics with RF, which is consistent previous study. The spiked shape voltage appeared at i = 0.25-0.35. This means the voltage has sensitive initial condition. Hence, the voltage is suggested chaotic behavior in this region.

Thereafter, we computed the Lyapunov exponent λ to judge the presence of a chaotic behavior. The λ is a factor that characterizes the rate of separation of infinitesimally close trajectories in a dynamical system. Therefore, the voltages are chaotic or non-chaotic, when λ is positive or negative. Figure 1(c) shows current dependence of the λ. In Fig. 1(c), the λ is positive at spike voltage region. This is suggested that chaotic voltage appeared in this region.

Further investigation, in the case of λ is positive, power spectrum of output voltage was calculated. Less than irradiation frequency, the spectrum is independent of frequency. i.e. the white noise region appeared. In other words, it is unpredictable random number can be generated. The generation rate is less than the irradiation frequency. Therefore, we propose white noise region broad by increasing irradiation frequency. For high-speed random number generation, irradiation frequency is increased to THz range from conventional several tens GHz. By the way, intrinsic Josephson junction (IJJ) stacks can emit the THz electromagnetic wave, which is coherent, continuous and monochromaticity[2]. The IJJs are atomically and naturally stacked in cuprate superconductor such as Bi-2212 single crystal. Therefore, we assumed the RF source is the IJJ emitter because the high-speed operation of random number generators is expected possibility.

We are planning the mesa-type sample for high speed random number generators. Specifically, the chaos generation mesa and THz emission mesa are fabricated on same superconductor chip. It makes the random-number generator using RF irradiated JJ can not only be realized but also compact and high-speed operating device.

In this presentation, we will focus on and report the random number generation rate using JJ under irradiation THz electromagnetic wave. In addition, we will discuss the quality of generated random numbers from output voltage of JJ using statistical test.

[1] R. L. Kautz et al., Journal of Applied Physics 57, 875 (1985).

[2] L. Ozyuzer et al., Science, 318, (2007).

EDP2-9

Experimental quantum computational chemistry with optimized unitary coupled cluster ansatz

13:15-14:45 Dec.4

*Haoran Qian

University of Science and Technology of China

Quantum computational chemistry has emerged as a potential application of quantum computing. Hybrid quantum-classical computing methods, such as variational quantum eigensolvers, have been designed as promising solutions to quantum chemistry problems. Nonetheless, challenges due to theoretical complexity and experimental imperfections hinder progress in achieving reliable and accurate results. Experimental works for solving electronic structures are consequently still restricted to non-scalable or classically simulable ansatz or limited to a few qubits with large errors. Here, we address the critical challenges associated with solving molecular electronic structures using noisy quantum processors. Our protocol presents improvements in the circuit depth and running time, key metrics for chemistry simulation. Through systematic hardware enhancements and the integration of error-mitigation techniques, we overcome theoretical and experimental limitations and successfully scale up the implementation of variational quantum eigensolvers with an optimized unitary coupled cluster ansatz to 12 qubits. We produce high-precision results of the ground-state energy for molecules with error suppression by around two orders of magnitude. Our work demonstrates a feasible path towards a scalable solution to electronic structure calculation.

EDP2-10

Design of a Superconducting Stochastic Adder Without Utilizing Random Number Train as Its Control Signal

13:15-14:45 Dec.4

*Yuya Mandai1, Nobuyuki Yoshikawa1,2,3, Yuki Yamanashi1,2,3

Department of Electrical and Computer Engineering, Yokohama National University, 79-5 Tokiwadai, Hodogaya, Yokohama, Kanagawa, 240-8501 & Japan1

Institute of Advanced Sciences, Yokohama National University, 79-5 Tokiwadai, Hodogaya, Yokohama, Kanagawa, 240-8501 & Japan2

Institute for Multidisciplinary Sciences, Yokohama National University, 79-5 Tokiwadai, Hodogaya, Yokohama, Kanagawa, 240-8501 & Japan3

Stochastic computing expresses a number in terms of the probability of a “1” occurring in a binary number sequence. The advantage of stochastic computing is that the basin arithmetic operation can be performed with the small number of logic gates. Another major advantage of the stochastic computing is that the weight of each bit in the stochastic number sequence is the same. The influences in calculation error due to bit flipping is small. This method can be applied in areas where calculation errors is acceptable. However, the calculation time of the stochastic arithmetic is long due to the signal expression by the long number sequence. We think single-flux quantum (SFQ)-based stochastic circuits can solve the problem of the long computation time.

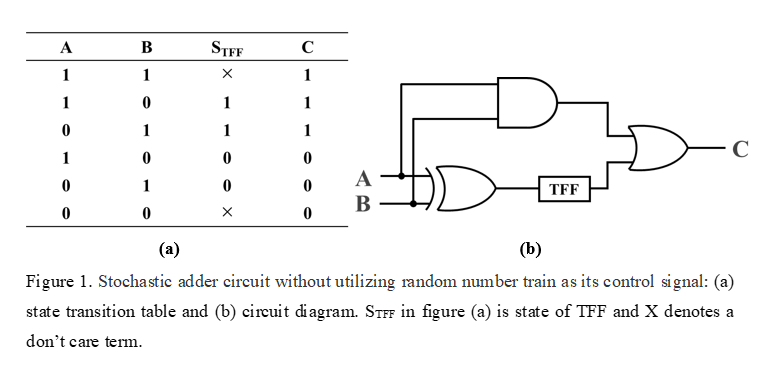

In the case of unipolar expression, the stochastic addition is performed by a multiplexer with random number sequence as the control signal. With finite number sequence length, control signal causes calculation errors. A stochastic adder circuit that does not require the control signal input has been proposed in the CMOS circuit [1]. Since this circuit does not require a control signal input, an area-saving adder can be realized. This circuit consists of a multiplexer, an exclusive-OR (XOR) gate and a toggle flip-flop (TFF).

In this study, we designed the SFQ stochastic adder by modifying the adder proposed in [1]. Figure 1(a) shows the state transition table of the stochastic adder without control signal. According to this table, we realized that the use of the multiplier is not required. Based on this concept, we designed the SFQ stochastic adder as shown in figure 1(b). We could eliminate AND and NOT gate from the adder previously proposed. We designed the SFQ stochastic adder, targeting operating frequency of 50 GHz using the AIST 10 kA/cm2 Nb high-speed process [2]. The number of Josephson junctions and circuit area of the designed SFQ stochastic adder is 79 and 0.24 mm × 0.3 mm, respectively.

In the circuit simulation, the input stochastic number sequences were generated using a superconductor random number generator (SRNG) [3]. We used JoSIM [4] to simulate the circuit and confirmed correct operation of the designed circuit at the 50 GHz. The maximum operating frequency is 90 GHz. This circuit had a significantly reduced calculation error compared to the multiplexer-based stochastic adder that requires random number sequence as the control signal. We think this adder enables us to design SFQ stochastic arithmetic circuits efficiently.

[1] V. T. Lee, A. Alaghi, J. P. Hayes, V. Sathe and L. Ceze, "Energy-efficient hybrid stochastic-binary neural networks for near-sensor computing," Design, Automation & Test in Europe Conference & Exhibition (DATE), Lausanne, Switzerland, pp. 13-18, 2017.

[2] M. Hidaka and S. Nagasawa, “Fabrication process for superconducting digital circuits,” IEICE Trans. Electron., vol. E104-C, pp. 405-410, Sep. 2021.

[3] Y. Yamanashi and N. Yoshikawa, “Superconductive Random Number Generator Using Thermal Noises in SFQ Circuits,” IEEE Trans. Appl. Supercond., vol. 19, no. 3, pp. 630-633, Jun. 2009.

[4] J. A. Delport, K. Jackman, P. l. Roux and C. J. Fourie, "JoSIM-Superconductor SPICE Simulator," IEEE Trans. Appl. Supercond., vol. 29, no. 5, pp. 1-5, Aug. 2019.

This work was supported by KAKENHI 22H01542 and 24H00311. The authors thank Naoki Ishikawa for fruitful discussion. The circuits were fabricated in the clean room for analog-digital superconductivity (CRAVITY) of National Institute of Advanced Industrial Science and Technology (AIST) with the high-speed standard process (HSTP).

Keywords: SFQ circuit, stochastic computing

EDP2-11

Hardware random number generator with a complementary structure using Josephson oscillation and SFQ logic circuits

13:15-14:45 Dec.4

*Takeshi Onomi, Shogo Yoshida

Fukuoka Institute of Technology

Random number generators are often needed to execute scientific software simulations, statistical analysis, cryptography and various fields of data processing algorithms. High-speed random number generations are usually implemented by using hardware random number generators (HRNGs) based on some uncertain physical phenomenon to get the source of random numbers. We have proposed an oscillator-based RNG using Josephson oscillation and single flux quantum (SFQ) logic circuits as such one of HRNGs [1]. The proposed HRNG has already been designed, fabricated using Nb/AlOx/Nb junction circuit technology and successfully tested. Though the HRNG generates stochastic binary numbers of “0” or “1” with the ratio of 50:50, the ratio may slightly shift from the ideal ratio due to variations of circuit parameters or the change of power supply voltage. In this report, a HRNG with a complementary structure is proposed to reduce simply such shifting from the ideal ratio of binary numbers. The proposed structure of a HRNG consists of two HRNGs which are an original one and another one with inverted outputs. This combination of two HRNGs is aimed at the generation ratio of random numbers compensated each other. The proposed HRNG is designed using process parameters of the AIST Nb high-speed standard process (HSTP) [2] with 10 kA/cm2 Nb/AlOx/Nb junctions. The improvement of the bias dependence of the random number generation rate is confirmed by numerical simulations of the designed circuits. Furthermore, the HRNG is fabricated using HSTP technology and tested. A random number generation based on a low-speed functional test is successfully confirmed. The measurement results show less bias dependence of the random number generation rate.

[1] T. Onomi and Y. Mizugaki, “Hardware Random Number Generator Using Josephson Oscillation and SFQ Logic Circuits,” IEEE Trans. Appl. Superconduct., vol. 30, no. 7, p. 1301305, Oct. 2020.

[2] Takeuchi, N., S. Nagasawa, F. China, T. Ando, M. Hidaka, Y. Yamanashi, and N. Yoshikawa, “Adiabatic quantum-flux parametron cell library designed using a 10 kA cm-2 niobium fabrication process," Supercond. Sci. Technol., Vol. 30, 035002, 2017.

This research was supported by JSPS KAKENHI Grant Numbers 18K11231 and 23K11042. This research was partly supported by VLSI Design and Education Center (VDEC), the University of Tokyo, in collaboration with Cadence Design Systems, Inc. The circuits were fabricated in the clean room for analog-digital superconductivity (CRAVITY) of the National Institute of Advanced Industrial Science and Technology (AIST) with HSTP. The authors thank Prof. Y. Mizugaki for technical supports of the low-temperature measurements.

EDP2-12

Prototyping of BSCCO/semiconductor heterojunctions using MOD method

13:15-14:45 Dec.4

*Yasuyuki Yamada1, Masato Nobushima1, Hiromu Kasai1, Shu Ikura1

Department of Innovative Electrical and Electronic Engineering, National Institute of Technology, Oyama College, 771 Nakakuki, Oyama, Tochigi 323-0806, Japan1

Superconductor/semiconductor heterojunction is expected to exhibit various photoresponse characteristics when forming Schottky or pn junctions. Additionally, the formation of ohmic contacts plays a crucial role in injecting carriers into the semiconductor, which is particularly important when forming a pn junction directly on the superconductor. In either case, it is advantageous from the perspective of device design flexibility to be able to deposit both p-type and n-type semiconductor thin films on the same type of superconductor, and to perform thin film deposition and microfabrication using methods that are environmentally friendly and simple. Regarding superconducting thin films, we have successfully prepared Bi2Sr2CaCu2O8+δ (BSCCO) using the metal-organic decomposition (MOD) method [1,2] and have also succeeded in forming bridges with a minimum width of 75μm using citric acid etching [3]. For semiconductor thin films, we have been prepared them by the MOD method and evaluating their band gaps and transmittance. Based on these insights, we are currently attempting to prepare superconductor/semiconductor heterojunctions using the MOD method. In this report, we present (1) that the BSCCO/CuxO junction, as a BSCCO/p-type semiconductor heterojunction, forms a good ohmic contact, and (2) our attempts to prepare BSCCO/n-type semiconductor heterojunctions. In this study, ZnO and NbOx were used as n-type semiconductors.

For the deposition of BSCCO, CuxO, ZnO, and NbOx thin films, we used solutions from High Purity Chemical Laboratory Co., Ltd.: BSCCO solution (SK-BSCCO008), Cu-O solution (Cu-03A), Zn-O solution (Zn-05), and Nb-O solution (Nb-05), respectively. MgO (100) or SrTiO3 (100) substrates with dimensions of 10×10×0.5 mm were used. A typical preparation process is as follows:

1. Use a spin coater to apply the first layer solution over the entire substrate.

2. Heat-treat the substrate with the first layer solution in a muffle furnace.

3. Using wrap film or mending tape for masking, partially apply the second layer solution to approximately half of the substrate area using the spin coater.

4. Heat-treat the substrate with the second layer solution in the muffle furnace.

5. Attach terminals.

The spin coating was performed using the spin coater (ASC-300) from Able Co., Ltd., and the heat treatment was conducted using the muffle furnace (KDF-P70) from Denken Co., Ltd. For the prepared semiconductor thin films, transmittance was measured and the band gap was evaluated using a Tauc plot. The transmittance measurement was performed using a UV-Vis spectrophotometer (UVmini-1240) from Shimadzu Corporation. Details will be discussed in the presentation.

[1] Y. Yamada, T. Kato, T. Ishibashi, T. Okamoto, and N. Mori, AIP Advances 8, 015101 (2018)

[2] Y. Yamada, N. Mori, T. Atsumi, T. Kato, T. Ishibashi, Physics Procedia 65, 165 (2015)

[3] Y. Yamada, T. Okamoto, Journal of Physics: Conference Series 1590, 012046 (2020)

Keywords: BSCCO, metal-organic decomposition method, MOD, semiconductor, heterojunction