EDP2-3

Speed-Up and Delay Time Stabilization in Superconductor-Based Random Number Generation

13:15-14:45 Dec.4

*Rikuo Yamanaka1, Nobuyuki Yoshikawa1,2,3 and Yuki Yamanashi1,2,3

Department of Electrical and Computer Engineering, Yokohama National University, 79-5 Tokiwadai, Hodogaya, Yokohama, Kanagawa, 240-8501 & Japan1

Institute of Advanced Sciences, Yokohama National University, 79-5 Tokiwadai, Hodogaya, Yokohama, Kanagawa, 240-8501 & Japan2

Institute for Multidisciplinary Sciences, Yokohama National University, 79-5 Tokiwadai, Hodogaya, Yokohama, Kanagawa, 240-8501 & Japan3

Random number generators are indispensable circuits for applications such as cryptography and probabilistic computation. Superconductor-based random number generators (SRNGs) based on single-flux-quantum (SFQ) circuits are very powerful circuits for such applications because of their ultrahigh speed and compactness. While SRNGs have a very simple circuit configuration because they do not need to amplify noise, they also have the problem of unstable delay times. This makes the design of application circuits difficult and has negative effects such as a reduction in the overall throughput of the circuit.

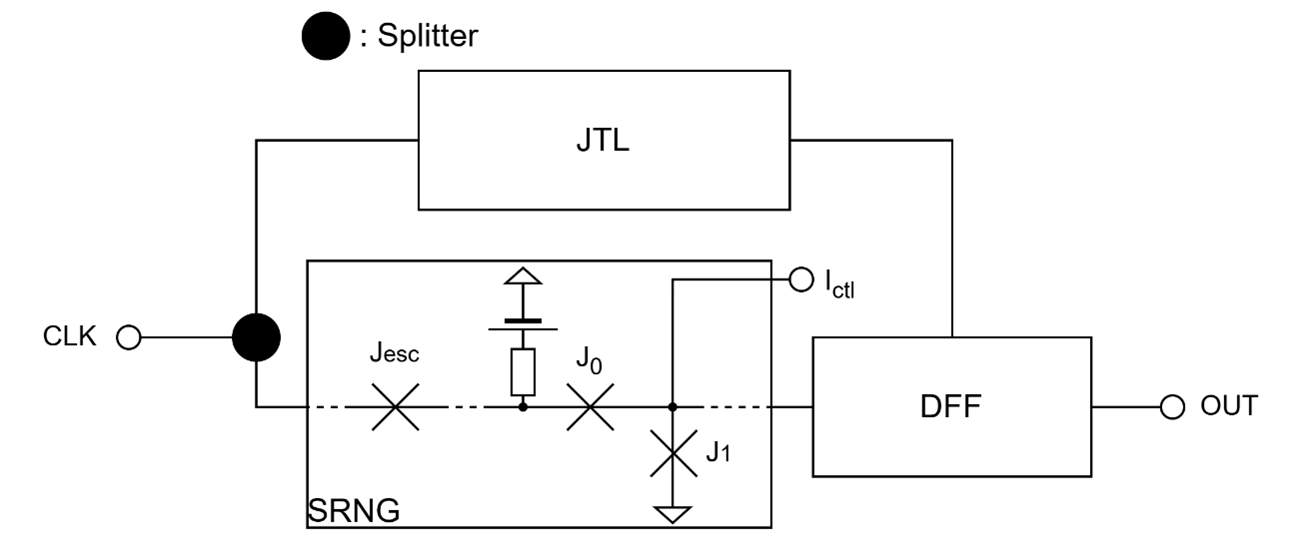

In this study, we optimized the circuit to stabilize the delay time of the SRNG as well as to reduce the delay time. Fig.1 shows the block diagram of the proposed circuit. One of the causes of delay variation is that when 1 is output, sometimes only J1 switches and sometimes both J1 and J0 switch. Therefore, in this study, the bias to the two Josephson junctions (JJs) was increased so that both JJs switch when all 1 are output, and Jesc is the JJ that prevents backflow of magnetic flux quantum when both JJs switch (when 1 is output). To further stabilize the delay, a Delay Flip-Flop (DFF) was connected to the output of the SRNG and adjusted so that the clock is input at the appropriate timing. To decrease the delay time, the driving power of the circuit was increased by increasing the bias and the critical current value of JJ in the front stage of the comparator (J1 and J0). the circuit was designed assuming an AISE 10 kA/cm^2 Nb high-speed process [2]. Simulations with thermal noise at 4.2 K using an analog circuit simulator reduced the maximum delay of the SRNG from 44.1 ps to 25.2 ps and the minimum delay from 26.0 ps to 23.6 ps. This result shows that the delay variation, which has been an issue with SRNGs, was reduced from 18.1 ps to 1.6 ps.

The delay variation of SRNGs was made close to that of general logic gates. This facilitates the design of application circuits for cryptography and probabilistic computation, etc. It is also expected to dramatically improve the overall throughput and maximum operating frequency of application circuits.

[1] Y. Yamanashi and N. Yoshikawa, “Superconductive Random Number Generator Using Thermal Noises in SFQ Circuits,” IEEE Trans. Appl. Supercond., vol. 19, no. 3, pp. 630–633, Jun. 2009.

[2] M. Hidaka and S. Nagasawa, “Fabrication process for superconducting digital circuits,” IEICE Trans. Electron., vol. E104–C, pp. 405–410, Sep. 2021.

This work was supported by KAKENHI 22H01542 and 24H00311.

Figure 1. Block diagram of circuit for stabilizing and speeding up SRNG.

Keywords: SFQ circuit, Random number generator