EDP2-10

Design of a Superconducting Stochastic Adder Without Utilizing Random Number Train as Its Control Signal

13:15-14:45 Dec.4

*Yuya Mandai1, Nobuyuki Yoshikawa1,2,3, Yuki Yamanashi1,2,3

Department of Electrical and Computer Engineering, Yokohama National University, 79-5 Tokiwadai, Hodogaya, Yokohama, Kanagawa, 240-8501 & Japan1

Institute of Advanced Sciences, Yokohama National University, 79-5 Tokiwadai, Hodogaya, Yokohama, Kanagawa, 240-8501 & Japan2

Institute for Multidisciplinary Sciences, Yokohama National University, 79-5 Tokiwadai, Hodogaya, Yokohama, Kanagawa, 240-8501 & Japan3

Stochastic computing expresses a number in terms of the probability of a “1” occurring in a binary number sequence. The advantage of stochastic computing is that the basin arithmetic operation can be performed with the small number of logic gates. Another major advantage of the stochastic computing is that the weight of each bit in the stochastic number sequence is the same. The influences in calculation error due to bit flipping is small. This method can be applied in areas where calculation errors is acceptable. However, the calculation time of the stochastic arithmetic is long due to the signal expression by the long number sequence. We think single-flux quantum (SFQ)-based stochastic circuits can solve the problem of the long computation time.

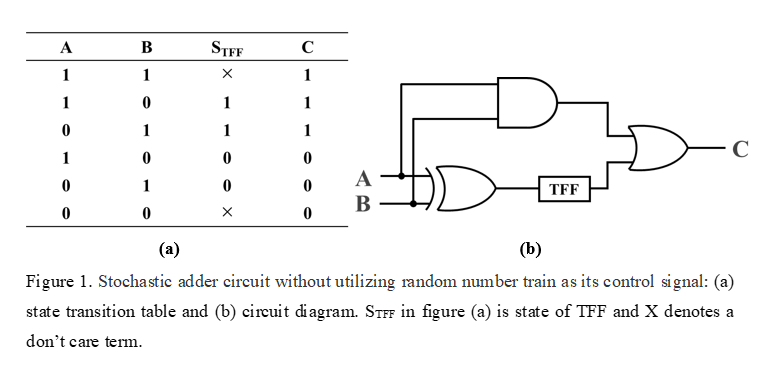

In the case of unipolar expression, the stochastic addition is performed by a multiplexer with random number sequence as the control signal. With finite number sequence length, control signal causes calculation errors. A stochastic adder circuit that does not require the control signal input has been proposed in the CMOS circuit [1]. Since this circuit does not require a control signal input, an area-saving adder can be realized. This circuit consists of a multiplexer, an exclusive-OR (XOR) gate and a toggle flip-flop (TFF).

In this study, we designed the SFQ stochastic adder by modifying the adder proposed in [1]. Figure 1(a) shows the state transition table of the stochastic adder without control signal. According to this table, we realized that the use of the multiplier is not required. Based on this concept, we designed the SFQ stochastic adder as shown in figure 1(b). We could eliminate AND and NOT gate from the adder previously proposed. We designed the SFQ stochastic adder, targeting operating frequency of 50 GHz using the AIST 10 kA/cm2 Nb high-speed process [2]. The number of Josephson junctions and circuit area of the designed SFQ stochastic adder is 79 and 0.24 mm × 0.3 mm, respectively.

In the circuit simulation, the input stochastic number sequences were generated using a superconductor random number generator (SRNG) [3]. We used JoSIM [4] to simulate the circuit and confirmed correct operation of the designed circuit at the 50 GHz. The maximum operating frequency is 90 GHz. This circuit had a significantly reduced calculation error compared to the multiplexer-based stochastic adder that requires random number sequence as the control signal. We think this adder enables us to design SFQ stochastic arithmetic circuits efficiently.

[1] V. T. Lee, A. Alaghi, J. P. Hayes, V. Sathe and L. Ceze, "Energy-efficient hybrid stochastic-binary neural networks for near-sensor computing," Design, Automation & Test in Europe Conference & Exhibition (DATE), Lausanne, Switzerland, pp. 13-18, 2017.

[2] M. Hidaka and S. Nagasawa, “Fabrication process for superconducting digital circuits,” IEICE Trans. Electron., vol. E104-C, pp. 405-410, Sep. 2021.

[3] Y. Yamanashi and N. Yoshikawa, “Superconductive Random Number Generator Using Thermal Noises in SFQ Circuits,” IEEE Trans. Appl. Supercond., vol. 19, no. 3, pp. 630-633, Jun. 2009.

[4] J. A. Delport, K. Jackman, P. l. Roux and C. J. Fourie, "JoSIM-Superconductor SPICE Simulator," IEEE Trans. Appl. Supercond., vol. 29, no. 5, pp. 1-5, Aug. 2019.

This work was supported by KAKENHI 22H01542 and 24H00311. The authors thank Naoki Ishikawa for fruitful discussion. The circuits were fabricated in the clean room for analog-digital superconductivity (CRAVITY) of National Institute of Advanced Industrial Science and Technology (AIST) with the high-speed standard process (HSTP).

Keywords: SFQ circuit, stochastic computing