EDP1-5

Monolithic integrated superconducting nanowire digital encoder and its application in reading out a SNSPD array

13:30-15:00 Dec.3

*Yanghui Huang1, Qingyuan Zhao1,2

Research Institute of Superconductor Electronics (RISE), School of Electronic Science and Engineering, Nanjing University, Nanjing, Jiangsu 210023, China1

Purple Mountain Laboratories, Nanjing, Jiangsu 211111, China2

As reported in the IEEE International Roadmap for Devices and Systems 2022 (IRDS), superconducting digital circuits are one of the most promising technological method due to their exceptional operational speed and low power consumption. Superconducting nanowire cryotron (nTron) is a three-terminal device with a feature size of around 100 nanometers, fabricated by superconducting thin films. When a current is injected into the gate, the channel is transited from superconducting state to highly resistive normal state, which enables nTron to generate an amplified output pulse governed by gate input.

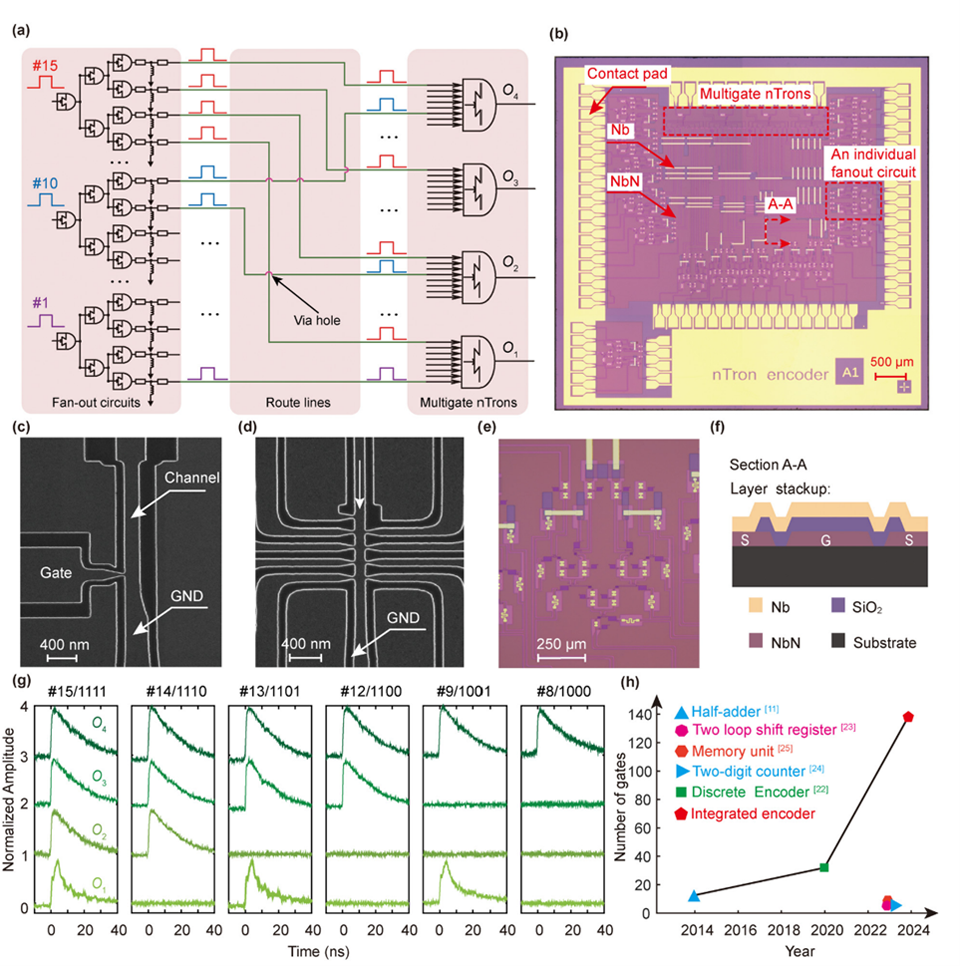

Attribute to its high output impedance, transistor-like operation logic and low power consumption, nTrons have been demonstrated in driving low-temperature COMS transistors, building neural networks, reading out low-temperature detector arrays, etc. Exploring nTrons in digital integrated circuits and quantum circuits is promising but faces challenging in scalability. In this study, we demonstrate a monolithic integrated nTron-based binary encoder, which includes input fanout circuits, on-chip biasing, combinational logic routing and multi-gate nTrons. This monolithic nTron digital circuit comprises 137 nTron gates, 424 resistors, 274 inductors, and 64 vias, which is developed using a two-superconducting-layer fabrication process. The maximum bias margin is 28% for the fanout circuit and 60% for the multi-gate nTron when using a signal generator, while the minimum timing jitter is 40 ps. The total power dissipation mainly from biasing resistors is 19.6 μW, making it more power efficient than RSFQ encoders. This nTron encoder is used to digitize and read out a 15-pixel SNSPD array, of which the fired pixel position is encoded into 4-bit address, which shows a minimum readout error rate lower than 10-4 and reduces the readout RF lines from 15 to 4.

[1] Huang, Y.-H., Zhao, Q.-Y., Chen, S., Hao, H., Wang, H., Guo, J.-W., Tu, X.-C., Zhang, L.-B., Jia, X.-Q., Chen, J., Kang, L., & Wu, P.-H. (2023). Splitter trees of superconducting nanowire cryotrons for large fan-out. Applied Physics Letters, 122(9), 092601.

[2] Huang, Y.-H., Zhao, Q.-Y., Chen, S., Hao, H., Wang, H., Guo, J.-W., Tu, X.-C., Zhang, L.-B., Jia, X.-Q., Chen, J., Kang, L., & Wu, P.-H. (2023). Splitter trees of superconducting nanowire cryotrons for large fan-out. Applied Physics Letters, 122(9), 092601.

The authors have no conflicts to disclose.

Figure 1. Overview of the 4-bit encoder. (a) Schematic diagram of the encoder. (b) Microscope image of the monolithic nTron encoder. Scanning electron microscope images of a single-gate nTron (c) and a multi-gate nTron (d). (e) Microscope image of the fanout circuit. (f) Conceptual diagram of the multilayers for cross section A-A0 marked in (b). (g) Output waveforms for input ports #15/1111, #14/1110, #13/1101, #12/1100, #9/1001, and #8/1000. The waveforms are normalized and vertically shifted on the y axis for clarity. The waveform of O1 has a second rising edge overlapped on the first one, which is unusual in the case of the other three outputs. It is possibly caused by a fabrication defect along the channel of that multi-gate nTron, where the hotspot growth becomes discontinuous. (h) Trend of the number of gates in nTron digital circuits over reported time.

Keywords: Superconducting nanocrytron, Integrated encoder, Bit error rate, Superconducting nanowire single-photon detector (SNSPD) array.