EDP1-10

Error Reduction Method of an RSFQ Approximate Multiplier Using Double Operations

13:30-15:00 Dec.3

*Shogo Kato, Nobutaka Kito

Chukyo University, Toyota, Aichi, 470-0393 Japan

Rapid single-flux-quantum (RSFQ) circuits are gaining attention as ultra-fast and low-power computing devices. Multiplication is a fundamental arithmetic operation extensively used in scientific and technical applications, including artificial intelligence processing. Multipliers consume a large layout area. Minimizing the area of a multiplier to embed many ones in a chip is essential to improve computational performance. Therefore, many compact RSFQ multipliers have been investigated. Recently, approximate computing emerged as a technique to reduce circuit area. Several RSFQ designs utilizing approximate computation have been proposed. However, they introduce errors in computational results. A mitigation method is essential for critical parts in numerical error.

This presentation proposes a method to reduce error by double operations of the approximated multiplier presented in [1]. This multiplier calculates an n-bit integer multiplication in 2n cycles and outputs the upper n-bits of the integer multiplication result. It is suitable for multiplications with a smaller bit width. The method improves the accuracy of n-bit approximate multiplication results to 2n-bits using the approximate multiplier twice.

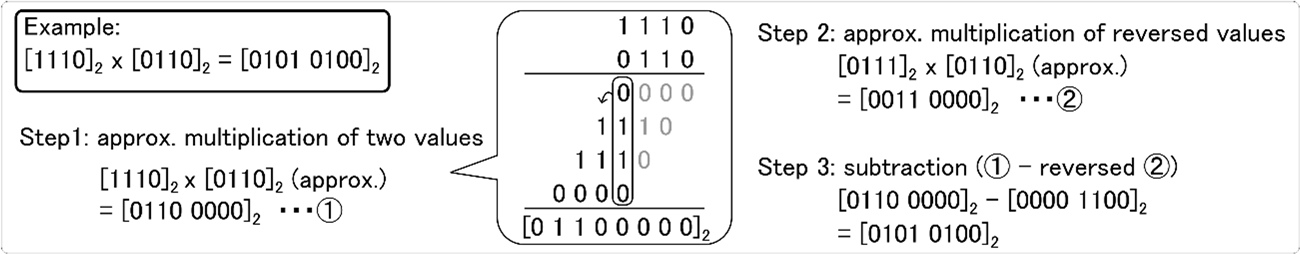

The method calculates the product of two integers, X and Y, in three steps. First, an approximate multiplication of X and Y is carried out with the approximate multiplier [1]. Then, an approximate multiplication of X's reversed bit order and Y's reversed bit order is carried out. Finally, the result is obtained by subtracting the reversed bit order of the latter result from the former.

This presentation also discusses circuit implementations of the proposed method. The method's multiplication can be realized using one or two approximate multipliers. The clock cycle latency of the latter case is almost the same as the original multiplier's latency, and the former's latency is almost double of the original multiplier's latency. This presentation discusses RSFQ circuit realizations for the subtraction in the final step for both cases.

The absolute error of results obtained with the proposed method was evaluated with exhaustive patterns through simulation for 4- to 6-bit multiplications. The evaluation results show that 70% of multiplication results are the same as the accurate multiplication results in 4-bit.

[1] N. Kito, R. Odaka, and K. Takagi, “Rapid Single-Flux-Quantum Truncated Multiplier Based on Bit-Level Processing,” IEICE Trans. Electronics, vol. E102-C, no. 7, pp. 607-611, 2019.

This research was supported by JSPS KAKENHI Grant Number JP22K11961.

Figure 1. Steps of the error reduction method using double approximate (approx.) multiplications.

Keywords: RSFQ circuits, Multiplier, Approximate computing